Техпроцессы меньше 1 нанометра ожидаются только к 2034 году — прогноз IMEC

Техпроцессы меньше 1 нм откладываются: IMEC прогнозирует их не раньше 2034 года

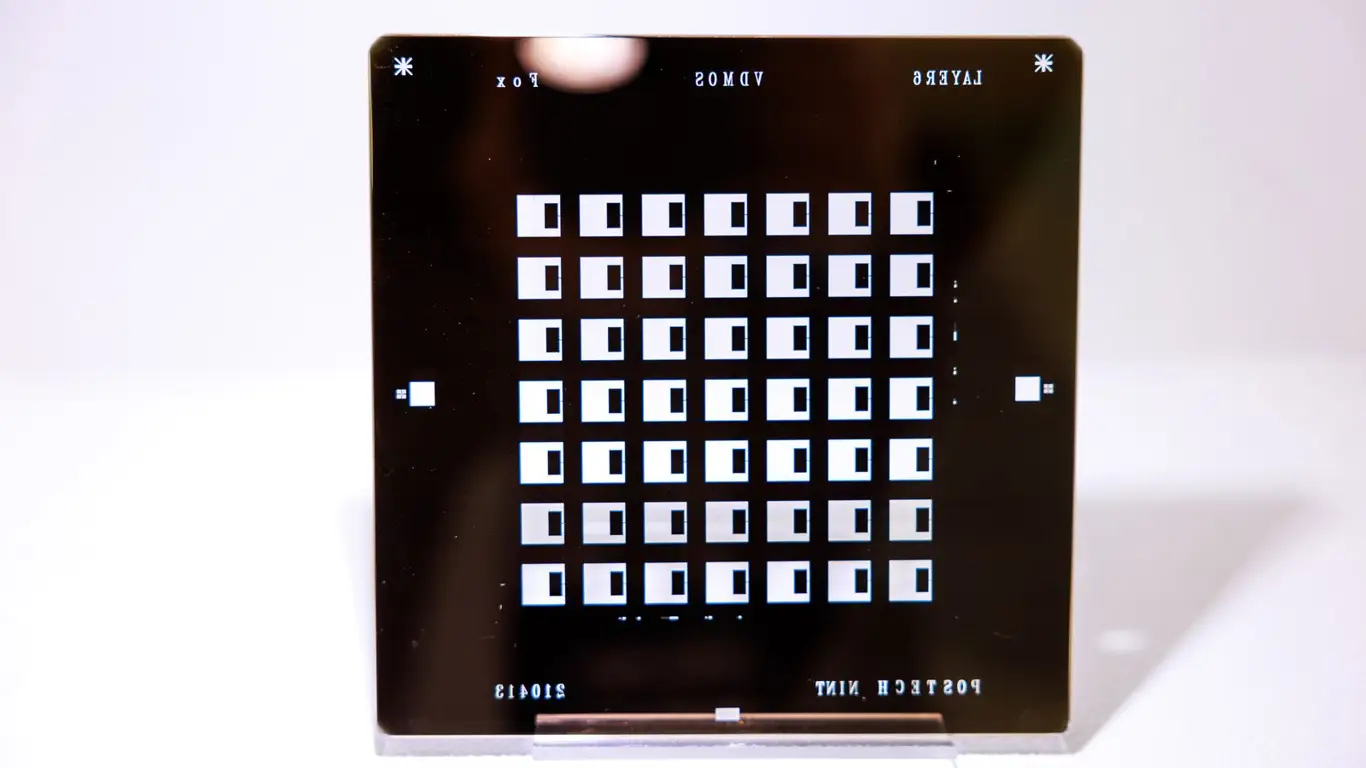

Согласно обновлённому прогнозу исследовательского центра IMEC, выход технологических процессов с нормами менее 1 нанометра откладывается как минимум до 2034 года. Развитие полупроводниковой отрасли замедлилось, хотя закон Мура, как отмечается, пока продолжает действовать. В ближайшие годы основное внимание будет уделено совершенствованию нанослойных транзисторов Gate-All-Around — например, 2-нм техпроцессу N2, за которым последуют узлы ангстремного класса, такие как A14 и A10. Как уточняется в документе, указанные даты отражают не поступление готовых изделий на рынок, а ориентировочные сроки завершения разработки технологий. Об этом сообщает издание pepelac.news.

Архитектурной основой для перехода к суб-нанометровому диапазону станут CFET-транзисторы, в которых p- и n-канальные элементы размещаются вертикально друг над другом. Первым таким техпроцессом должен стать A7 (0,7 нм), за ним к 2036 году ожидается A5, а к 2040-му — A3. В 2040-х годах, по мнению экспертов IMEC, могут появиться 2D FET-транзисторы на новых материалах. Предполагается, что около 2043 года они лягут в основу узла A2 (0,2 нм), а к 2046 году возможны и структуры с размером менее 0,2 нм. Однако все эти сроки носят исследовательский характер и могут корректироваться.

В центре подчёркивают, что для дальнейшего прогресса недостаточно одних лишь транзисторов. Ключевыми направлениями также становятся 2,5D- и 3D-упаковка, чиплеты, новые материалы для межсоединений, интегрированные регуляторы напряжения и более эффективные схемы питания. Именно combo этих технологий должно обеспечить развитие ИИ-ускорителей, HPC-систем и процессоров будущих поколений.